Uploads by Rlcude

Jump to navigation

Jump to search

This special page shows all uploaded files.

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

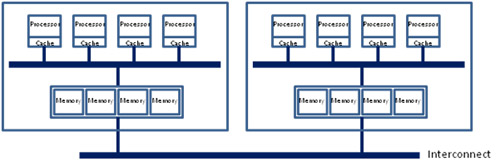

| 23:06, 21 November 2013 | UMA&NUMA.jpg (file) |  |

23 KB | The cross between the UMA and NUMA configurations. | 1 |

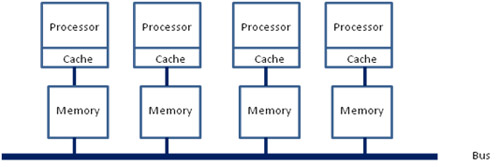

| 23:03, 21 November 2013 | NUMA.jpg (file) |  |

17 KB | A diagram of the NUMA memory configuration. | 1 |

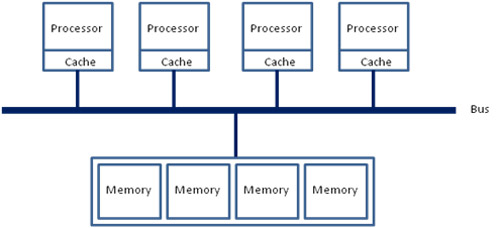

| 23:00, 21 November 2013 | UMA.jpg (file) |  |

19 KB | A diagram of the UMA system configuration. | 1 |

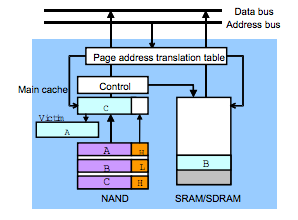

| 14:36, 24 September 2013 | NAND Organization.png (file) |  |

20 KB | This is the organizational structure of the NAND IXP embedded mobile system. Taken from A Low-cost Memory Architecture with NAND XIP for Mobile Embedded Systems by Chanik Park, Jaeyu Seo, Sunghwan Bae, Hyojun Kim, Shinhan Kim and Bumsoo Kim | 1 |

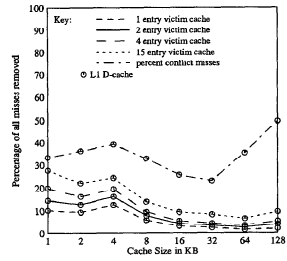

| 14:16, 24 September 2013 | Victim Cache Cache Size.png (file) |  |

28 KB | This graph demonstrates the correlation between victim cache performance and the size of the primary cache. Taken from Improving Direct-Mapped Cache Performance by the Addition of a Small Fully-Associative Cache and Prefetch Buffers by Jouppi. | 1 |

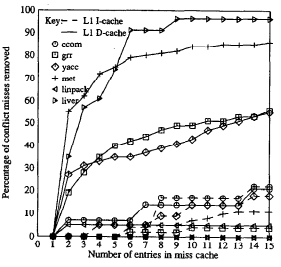

| 13:58, 24 September 2013 | Miss Cache Miss Ratios.png (file) |  |

34 KB | This graph illustrates the conflict misses avoided by using the miss cache scheme. Taken from Improving Direct-Mapped Cache Performance by the Addition of a Small Fully-Associative Cache and Prefetch Buffers by Jouppi. | 1 |

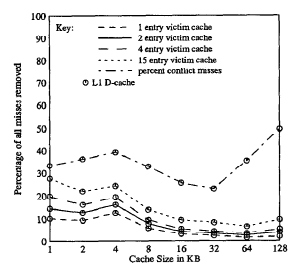

| 13:57, 24 September 2013 | Victim Cache Line Size.png (file) |  |

28 KB | This graph depicts the increase in productivity of the victim cache scheme as the line sizes increase. Taken from Improving Direct-Mapped Cache Performance by the Addition of a Small Fully-Associative Cache and Prefetch Buffers by Jouppi. | 1 |

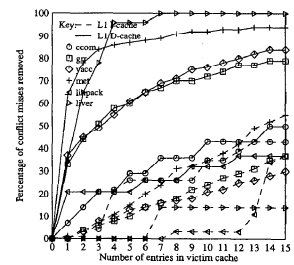

| 13:56, 24 September 2013 | Victim Cache Miss Ratios.png (file) |  |

37 KB | A graph depicting the amount of conflict misses that were avoided by using victim caching. Taken from Improving Direct-Mapped Cache Performance by the Addition of a Small Fully-Associative Cache and Prefetch Buffers by Jouppi. | 1 |

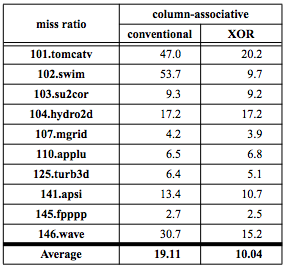

| 13:23, 24 September 2013 | XOR Miss Ratio Table.png (file) |  |

29 KB | This is a table taken from Eliminating Cache Conflict Misses Through XOR-Based Placement Functions by Antonio González, Mateo Valero, Nigel Topham and Joan M. Parcerisa. It illustrates the miss ratio differences between standard victim caching and combin | 1 |

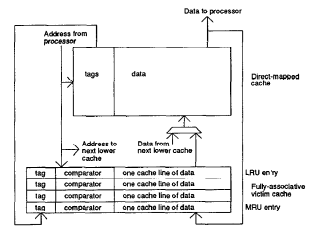

| 11:55, 24 September 2013 | Selective Victim Cache Organization.png (file) |  |

23 KB | This is an illustration of the organization of the selective victim caching process that was introduced in the paper Selective victim caching: a method to improve the performance of direct-mapped caches by Dimitrios Stiliadis and Anujan Varma. | 1 |

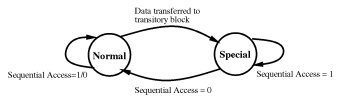

| 11:54, 24 September 2013 | Transitory Block Sequential Predictor.png (file) |  |

16 KB | This is an illustration of the interchange between the transitory block and the main cache when deciding if a block is part of a repeated sequential access from Selective victim caching: a method to improve the performance of direct-mapped caches by Dimit | 1 |

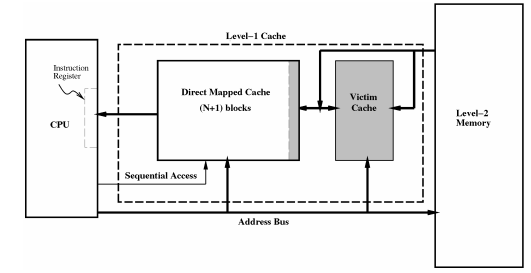

| 10:42, 24 September 2013 | Victim Cache Organization.png (file) |  |

25 KB | An illustration of victim cache organization from: Improving direct-mapped cache performance by the addition of a small fully-associative cache and prefetch buffers by Norman Jouppi. | 1 |

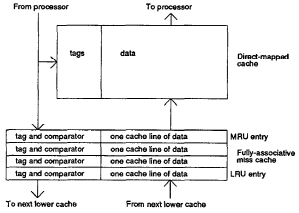

| 10:40, 24 September 2013 | Miss Cache Organization.png (file) |  |

24 KB | An illustration of how a miss cache is organized from: Improving direct-mapped cache performance by the addition of a small fully-associative cache and prefetch buffers by Norman Jouppi. | 1 |

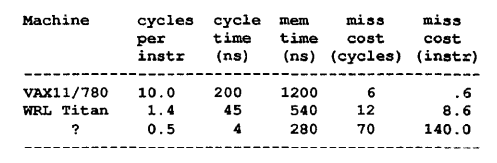

| 15:25, 17 September 2013 | Cost of cache misses from Jouppi.png (file) |  |

31 KB | Figure 1.1: This table was included in Jouppi's original paper to show the hinderance that cache misses were taking on newer machines. | 1 |