CSC/ECE 506 Spring 2012/8a cj: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

|||

| Line 12: | Line 12: | ||

=Protocol Performance= | =Protocol Performance= | ||

=References= | =References= | ||

# [http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4606981&tag=1] | # [http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4606981&tag=1 The research of the inclusive cache used in multi-core processor] | ||

Revision as of 13:30, 20 March 2012

MSI, MESI, MESIF, and MOESI protocols on real architectures

MSI Protocol

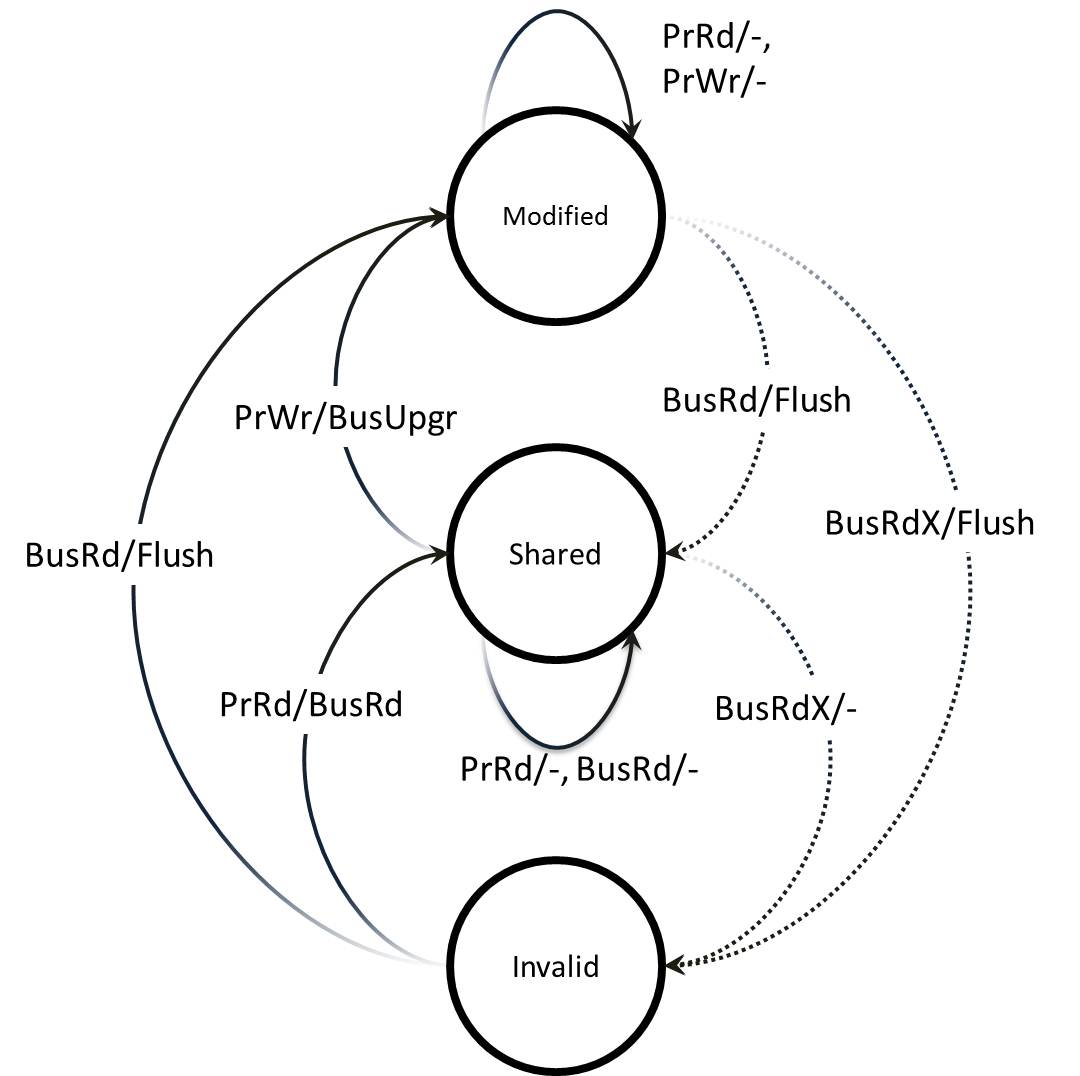

MESI Protocol

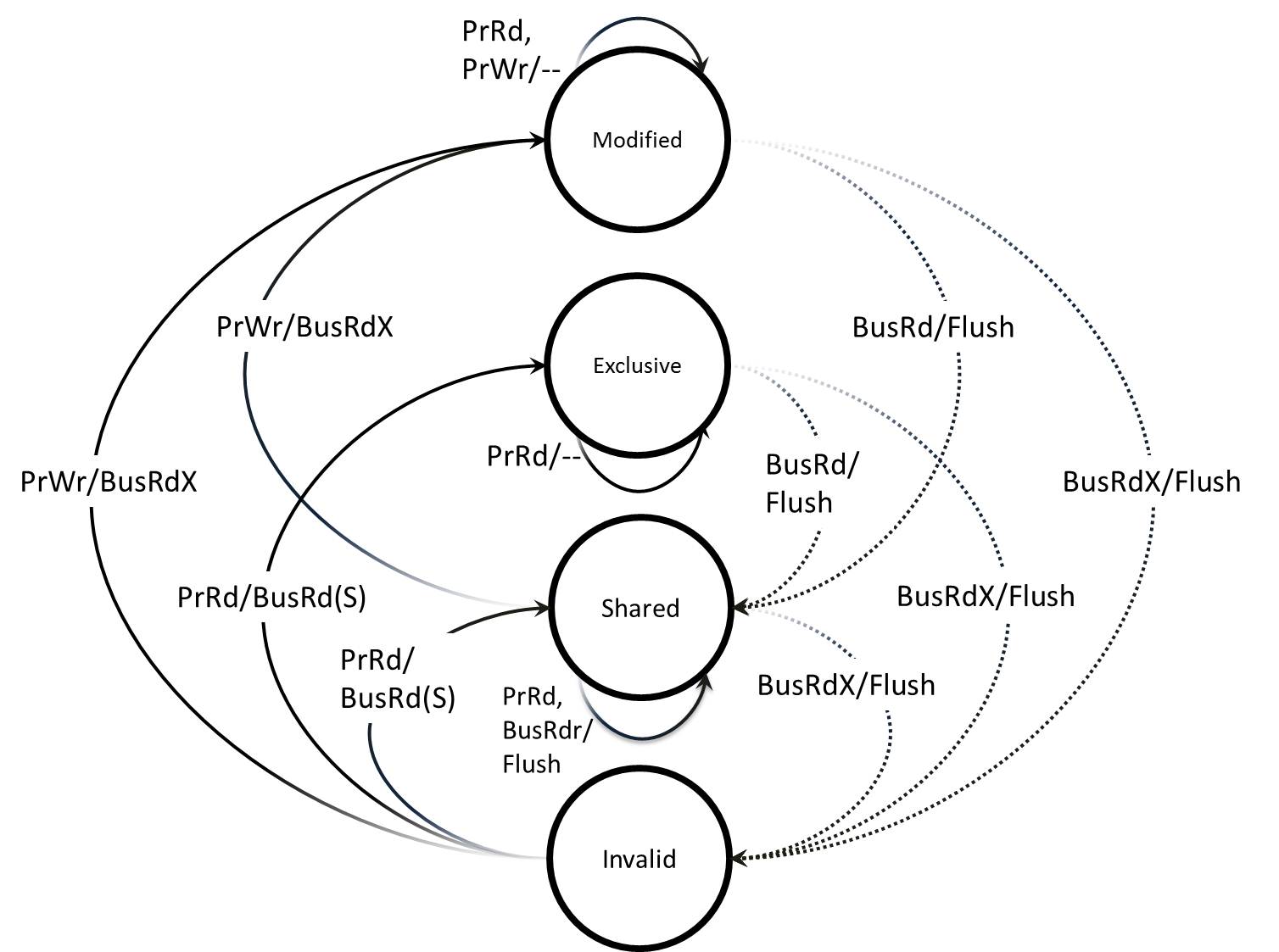

Five State Protocols

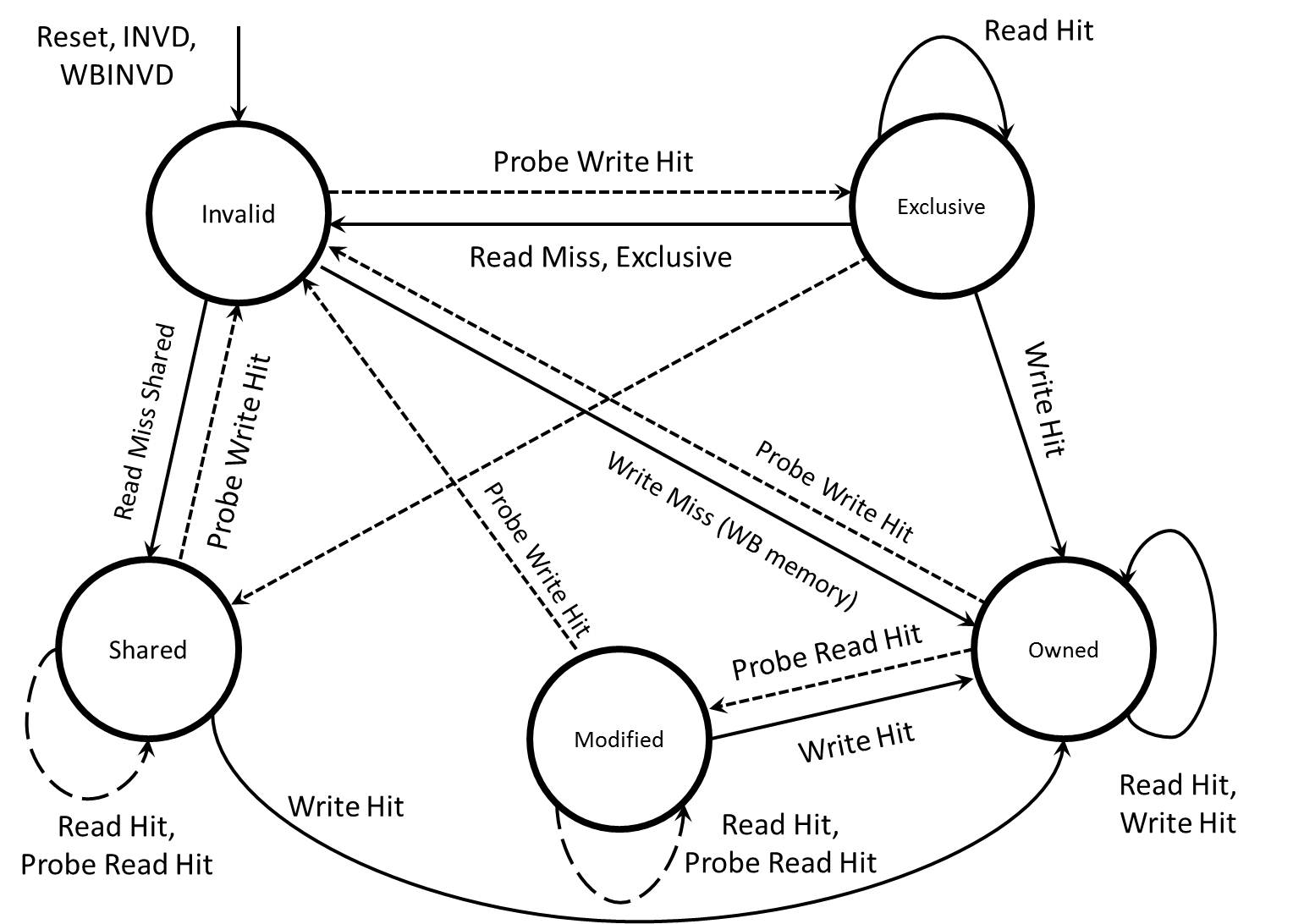

MOESI

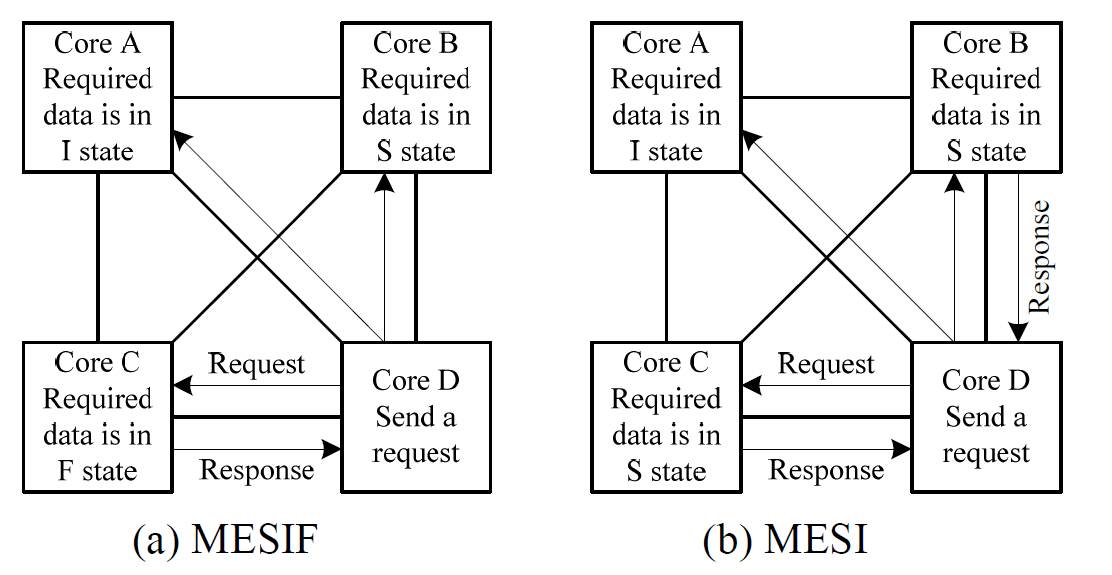

MESIF