CSC/ECE 506 Spring 2011/ch7 ss: Difference between revisions

| Line 8: | Line 8: | ||

[[Image:CCpic3.jpg|center]] | [[Image:CCpic3.jpg|center]] | ||

Thus, as evident from the above example, multiple copies of a block can easily get inconsistent. Hence, caches are critical to modern high-speed processors. The following section discusses the different solutions used to solve this problem. | |||

== Cache Coherence Solutions == | |||

Cache coherence solutions are mainly classified as - '''Software-based''' and '''hardware-based''' solutions. | |||

Software-based solutions are further classified as: | |||

* Compiler-based or with run-time system support | |||

* With or without hardware assist | |||

Hardware-based solutions can be differentiated as: | |||

* Shared caches or Snoopy schemes or Directory-based schemes | |||

* Write-through vs write-back protocols | |||

* Update vs invalidation protocols | |||

* Dirty-sharing vs. no-dirty-sharing protocols | |||

The main concern in case of software-based solutions is perfect information is needed at all times when memory aliasing and explicit parallelism are required.So, the focus is more on improving hardware-based solutions and they are more common. | |||

Revision as of 07:27, 13 March 2011

Though the migration from uniprocessor system to multiprocessing systems is not new, the world of parallel computers is undergoing a continuous change. Parallel computers, which started as high-end super-computing systems for carrying out huge calculations, are now ubiquitous and are present in all mainstream architectures for servers, desktops, and embedded systems. In order to design parallel architectures to meet programmer's needs and expectations more closely, exciting and challenging changes exist. The three main areas which are being considered by scientists today are: cache coherence, memory consistency and synchronization.

This article discusses these three issues and how they can be solved efficiently to meet programmer's requirements. A related topic - TLB coherence - is also dealth with. The wiki supplement also addresses the challenges that Peterson's algorithm demonstrates.

Cache Coherence

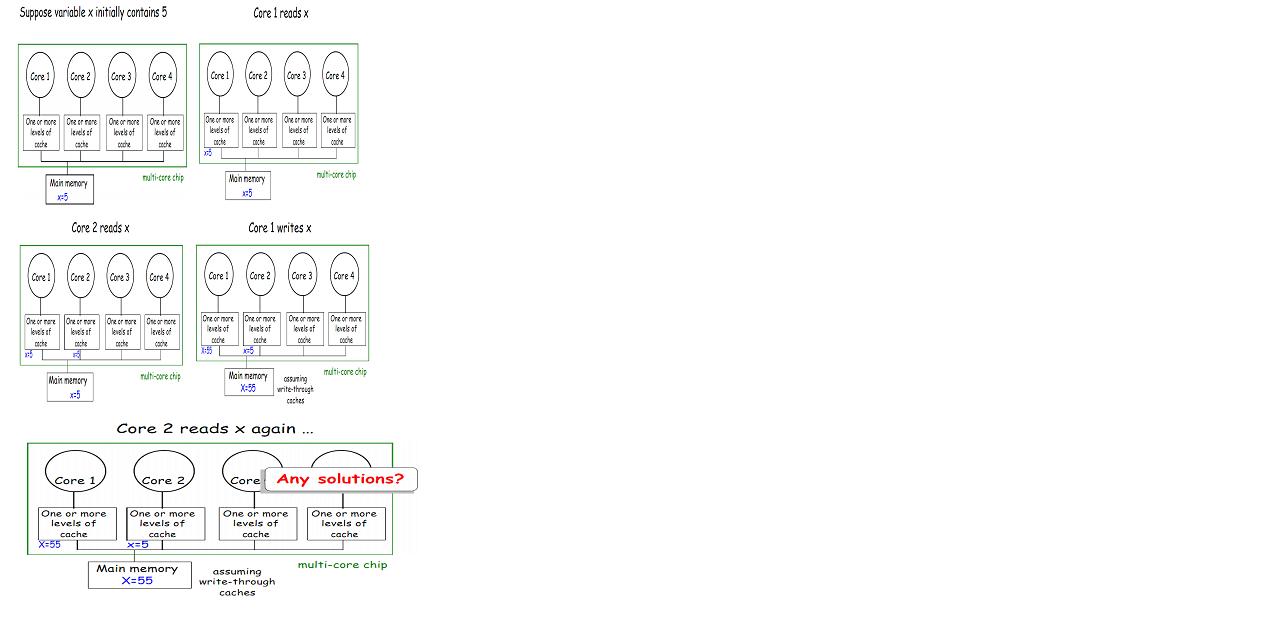

Here, by cache, we mean CPU cache. These are the small memories on or close to the CPU can operate faster than the much larger main memory.Cache coherency refers to the consistency of data stored in local caches of a shared resource. The following scenario shows the problems arising from inconsistent data when clients maintain caches of a common memory resource:

Thus, as evident from the above example, multiple copies of a block can easily get inconsistent. Hence, caches are critical to modern high-speed processors. The following section discusses the different solutions used to solve this problem.

Cache Coherence Solutions

Cache coherence solutions are mainly classified as - Software-based and hardware-based solutions.

Software-based solutions are further classified as:

- Compiler-based or with run-time system support

- With or without hardware assist

Hardware-based solutions can be differentiated as:

- Shared caches or Snoopy schemes or Directory-based schemes

- Write-through vs write-back protocols

- Update vs invalidation protocols

- Dirty-sharing vs. no-dirty-sharing protocols

The main concern in case of software-based solutions is perfect information is needed at all times when memory aliasing and explicit parallelism are required.So, the focus is more on improving hardware-based solutions and they are more common.