CSC/ECE 506 Spring 2011/6a ms: Difference between revisions

No edit summary |

|||

| Line 7: | Line 7: | ||

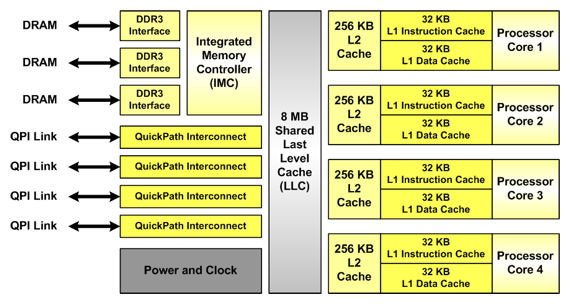

[[Image:Nahalem-cache.jpg|frame|center|Intel's Nehalem architecture, used on their core i7 processors]] | [[Image:Nahalem-cache.jpg|frame|center|Intel's Nehalem architecture, used on their core i7 processors]] | ||

==Modern Cache Architectures== | |||

To give an idea of typical cache sizes, examples of modern processor caches are given in the table below. | To give an idea of typical cache sizes, examples of modern processor caches are given in the table below. | ||

{| class="wikitable" border="1" | {| class="wikitable" border="1" | ||

|+Modern cache | |+Table 1: Modern cache architectures | ||

|- | |- | ||

! Vendor and Processor | ! Vendor and Processor | ||

| Line 133: | Line 134: | ||

=Write Policy= | =Write Policy= | ||

=Prefetching= | =Prefetching= | ||

=References= | |||

Revision as of 01:26, 1 March 2011

Cache Architecture

CPU caches are designed to mitigate the performance hit of reading and writing to main memory. Since main memory clock speeds are typically much slower than processor clock speeds, going to main memory for every read and write can result in a very slow system. Caches are constructed on the processor chip and take advantage of spatial and temporal locality to store data likely to be needed again by the processor.

Modern processors typically have two to three levels of cache. Each processor core has private level 1 (L1) data and instruction caches and a L2 combined data+instruction cache. Sometimes, a shared L3 cache is used to serve as an additional buffer between the cache and main memory. The figure below shows the cache hierarchy in a modern processor.

Modern Cache Architectures

To give an idea of typical cache sizes, examples of modern processor caches are given in the table below.

| Vendor and Processor | Cores | L1 cache | L2 cache | L3 cache | Date |

|---|---|---|---|---|---|

| Intel Pentium Dual Core | 2 | I: 32KB D: 32KB | 1MB 8-way set-associative | - | 2006 |

| Intel Xenon Clovertown | 2 | I: 4x 32KB D: 4x 32KB | 2x 4MB | - | January 2007 |

| Intel Xenon 3200 Series | 4 | 2x 4MB | - | January 2007 | |

| AMD Athlon 64 FX | 2 | I: 64KB D: 4KB 2-way set-associative | 1MB 16-way set-associative | - | May 2007 |

| AMD Athlon 64 X2 | 2 | I: 64KB D: 4KB 2-way set-associative | 512KB/1MB 16-way set-associative | 2MB | June 2007 |

| AMD Barcelona | 4 | I: 64KB D: 64KB | 512KB | 2MB | August 2007 |

| Sun Microsystems Ultra Sparc T2 | 8 | I: 16KB D: 8KB | 4MB 8 banks, 4-way set-associative | - | October 2007 |

| Intel Xeon Wolfdale DP | 2 | D: 96KB | 6MB | - | November 2007 |

| Intel Xeon Harpertown | 4 | D: 96KB | 2x 6MB | - | November 2007 |

| AMD Phenom | 4 | I: 64KB D: 64KB | 512KB | 2MB shared | November 2007, March 2008 |

| Intel Core 2 Duo | 2 | I: 32KB D: 32KB | 2-4MB 8-way set-associative | - | 2008 |

| Intel Penryn Wolfdale | 4 | 6-12MB | 6MB | March, August 2008 | |

| Intel Core 2 Quad Yorkfield | 4 | D: 96KB | 12MB | - | March 2008 |

| AMD Toliman | 3 K10 | I: 64KB D: 64KB | 512KB | 2MB shared | April 2008 |

| Azul Systems Vega 3 7300 Series | 864 | 768GB total | - | - | May 2008 |

| IBM RoadRunner | 8+1 | 32KB | 512KB | - | June 2008 |