CSC/ECE 506 Spring 2010/chapter 8: Difference between revisions

No edit summary |

|||

| Line 6: | Line 6: | ||

[[Image:Busbased SMP.jpg]] | [[Image:Busbased SMP.jpg]] | ||

Some of the popular bus based snooping protocols in some real time machines: | |||

States Access Type Invariant | |||

Modified read, write all other caches in I state | |||

Exclusive read, write all other caches in I state | |||

Owned read all other caches in I or S state | |||

Shared read no other cache in M or E state | |||

Invalid - - | |||

Revision as of 21:22, 26 March 2010

**Implementation of bus-based coherence protocols in real machines**

Introduction

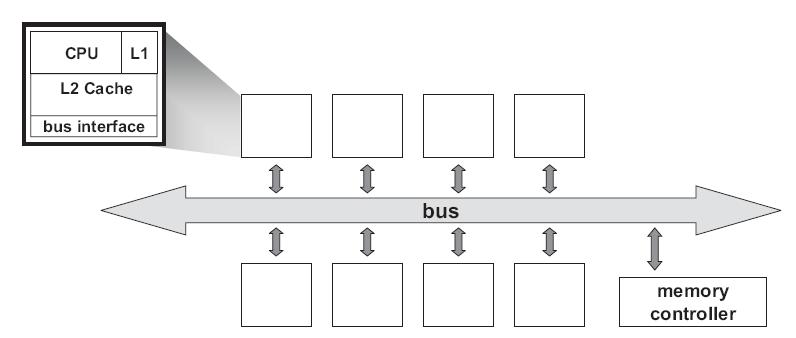

Most parallel software in the commercial market relies on the shared-memory programming model in which all processors access the same physical address space. And the most common multiprocessors today use SMP architecture which use a common bus as the interconnect. In the case of multicore processors (CMP) the SMP architecture applies to the cores treating them as separate processors. The key problem of shared-memory multiprocessors is providing a consistent view of memory with various cache hierarchies. This is called cache coherence problem. It is critical to achieve correctness and performance-sensitive design point for supporting the shared-memory model. The cache coherence mechanisms not only govern communication in a shared-memory multiprocessor, but also typically determine how the memory system transfers data between processors, caches, and memory.

Some of the popular bus based snooping protocols in some real time machines: States Access Type Invariant Modified read, write all other caches in I state Exclusive read, write all other caches in I state Owned read all other caches in I or S state Shared read no other cache in M or E state Invalid - -