Chp8 my: Difference between revisions

Jump to navigation

Jump to search

(→AMD) |

|||

| Line 38: | Line 38: | ||

====AMD==== | ====AMD==== | ||

AMD Opteron is using MOESI protocol for cache sharing. | AMD Opteron is using MOESI protocol for cache sharing. In addition to the four states in MESI, which is adopted by Intel for their Xeon processors, a fifth state "Owned" appears here representing data that is both modified and shared. Using MOESI, writing modified data back to main memory is avoided before being shared, which could save bandwidth and gain much faster access to users to the cache. | ||

[[Image:Opteron moesi.gif]] | [[Image:Opteron moesi.gif]] | ||

Revision as of 01:14, 26 March 2010

In computing, cache coherence (also cache coherency) refers to the consistency of data stored in local caches of a shared resource. Cache coherence is a special case of memory coherence.

Cache Coherence

Definition

Coherency protocol

MSI protocol

Intel

AMD

MESI protocol

In MESI protocol, there are four cache block status:

- 1. Modified (M): the cache block valid in only one cache and the value is like different from the main memory.

- 2. Exclusive (E): the cache block is valid and clean, but only resides in one cache.

- 3. Shared (S): the cache block is valid and clean, but may exist in multiple caches.

- 4. Invalid (I): the cache block is invalid.

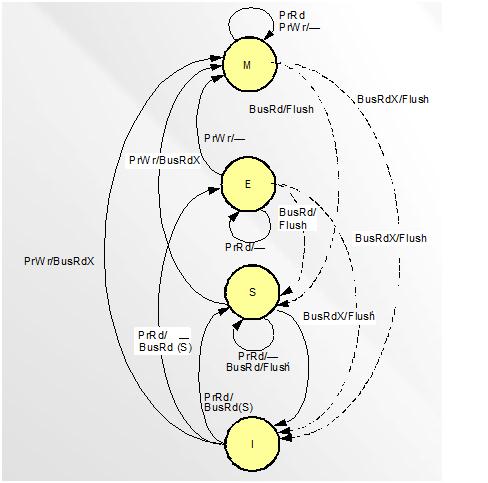

This figure shows the status change when bus traction generated.

Intel

AMD

MOESI protocol

Intel

AMD

AMD Opteron is using MOESI protocol for cache sharing. In addition to the four states in MESI, which is adopted by Intel for their Xeon processors, a fifth state "Owned" appears here representing data that is both modified and shared. Using MOESI, writing modified data back to main memory is avoided before being shared, which could save bandwidth and gain much faster access to users to the cache.