CSC/ECE 506 Spring 2012/8a cj: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| Line 11: | Line 11: | ||

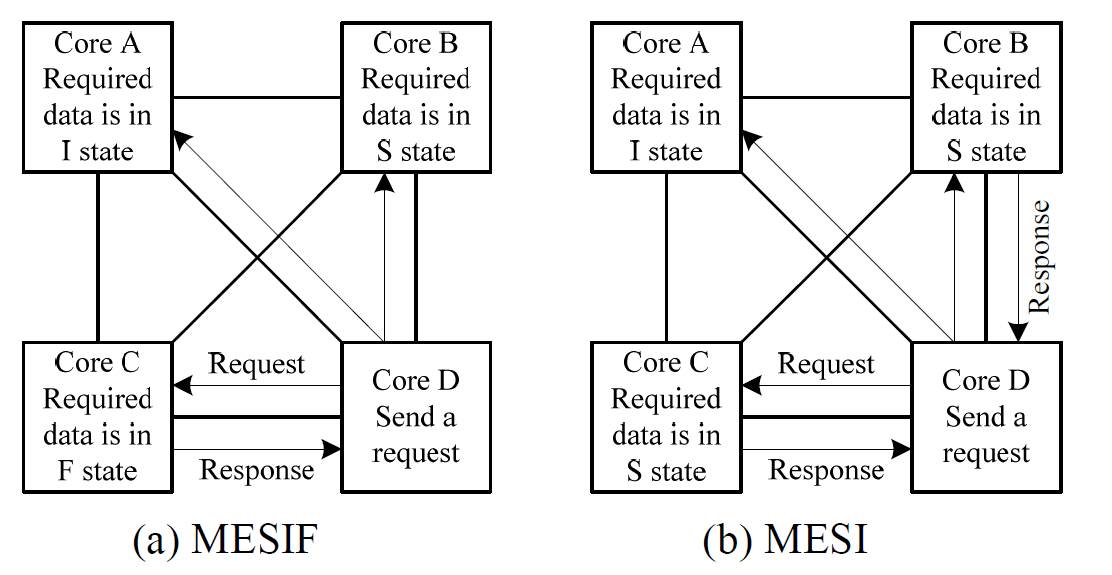

[[Image:MESIFVMESI.jpg|thumb|upright|center|450px|<b>Figure 4:</b> Reduced Traffic with MESIF Protocol [http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4606981&tag=1]]] | [[Image:MESIFVMESI.jpg|thumb|upright|center|450px|<b>Figure 4:</b> Reduced Traffic with MESIF Protocol [http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4606981&tag=1]]] | ||

=Protocol Performance= | =Protocol Performance= | ||

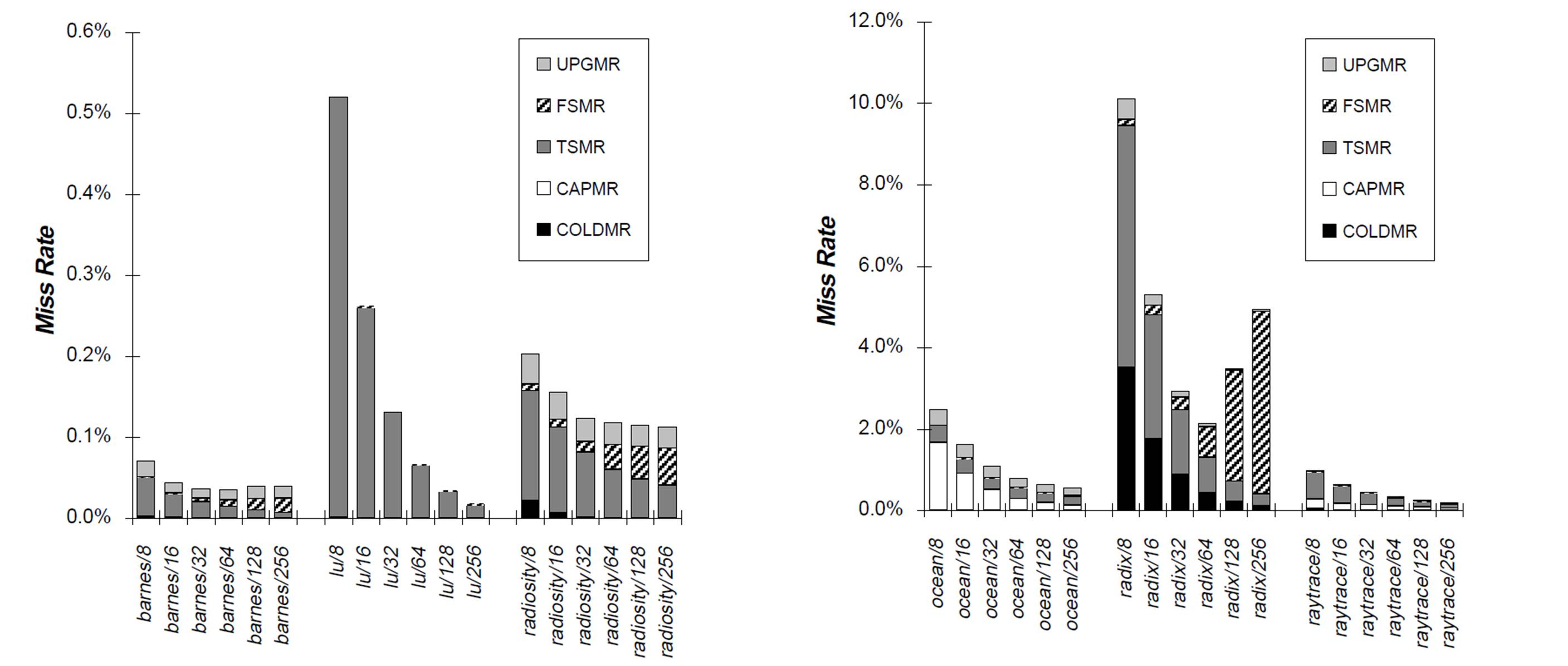

[[Image:TypeOfMiss.jpg|thumb|upright|center|450px|<b>Figure 5:</b> Type of Miss]] | [[Image:TypeOfMiss.jpg|thumb|upright|center|450px|<b>Figure 5:</b> Type of Miss [http://ams.ict.ac.cn/wp-content/uploads/2012/03/Parallel-computer-architecture.pdf]]] | ||

=References= | =References= | ||

# [http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4606981&tag=1 The research of the inclusive cache used in multi-core processor] | # [http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4606981&tag=1 The research of the inclusive cache used in multi-core processor] | ||

# [http://books.google.com/books?id=MHfHC4Wf3K0C&pg=PA620&lpg=PA620&dq=Culler+and+Singh+1998&source=bl&ots=1KHO-a3JXQ&sig=ZEZ0Xjer6Y4IJJgm6GXjnerYnkI&hl=en&sa=X&ei=ko9oT4LfH4aPsQKItY2wCQ&ved=0CCsQ6AEwAQ#v=onepage&q=Culler%20and%20Singh%201998&f=false] | |||

Revision as of 14:09, 20 March 2012

MSI, MESI, MESIF, and MOESI protocols on real architectures

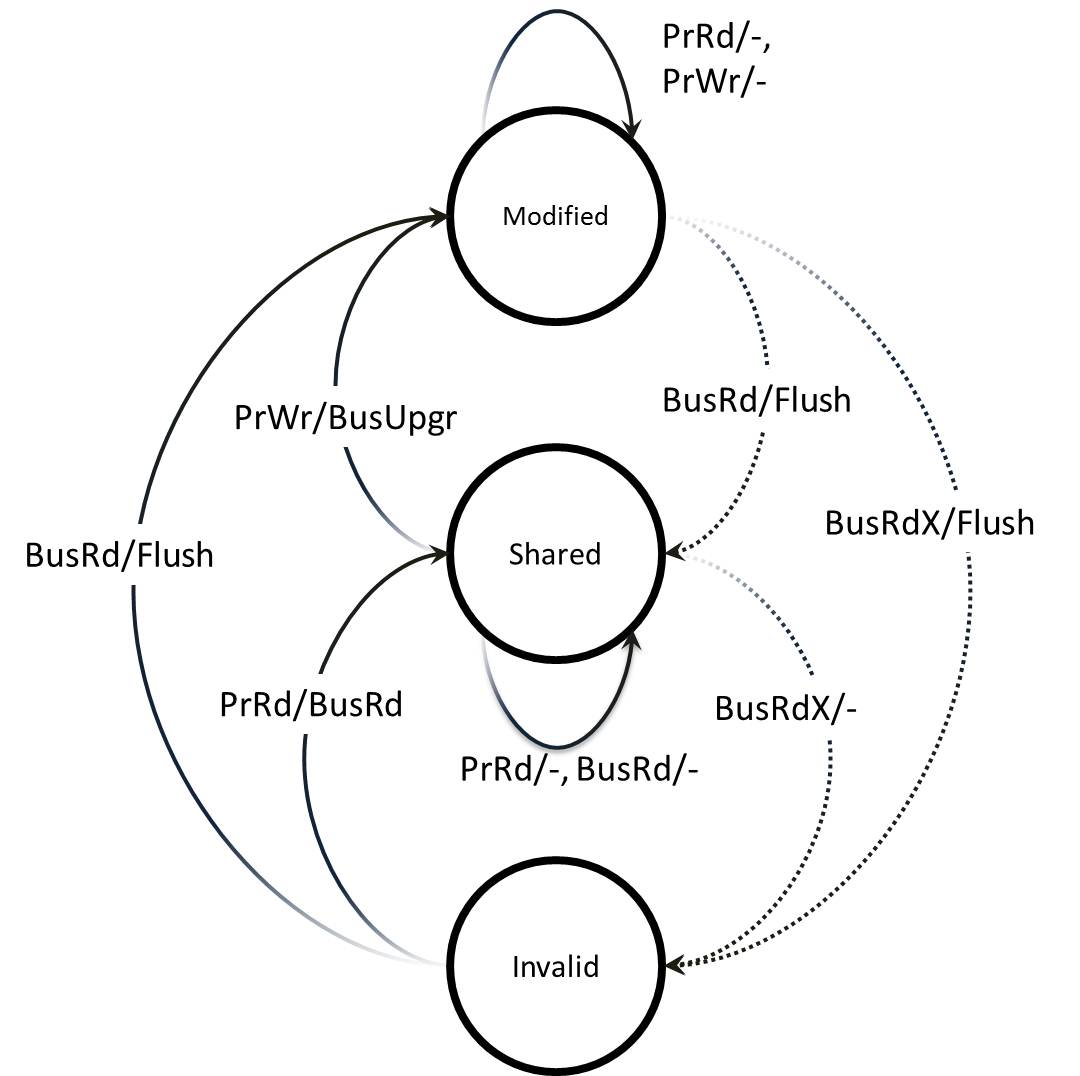

MSI Protocol

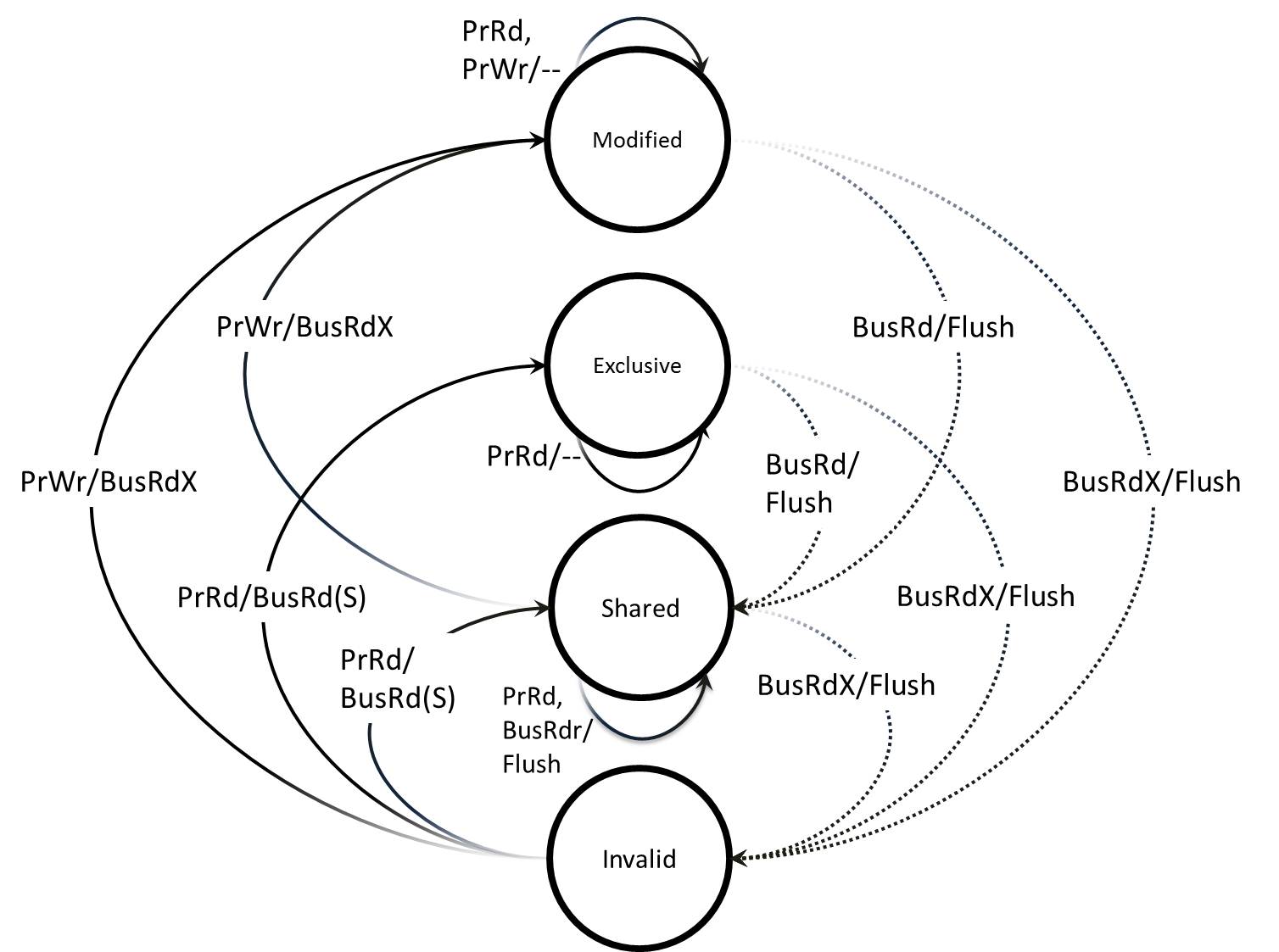

MESI Protocol

Five State Protocols

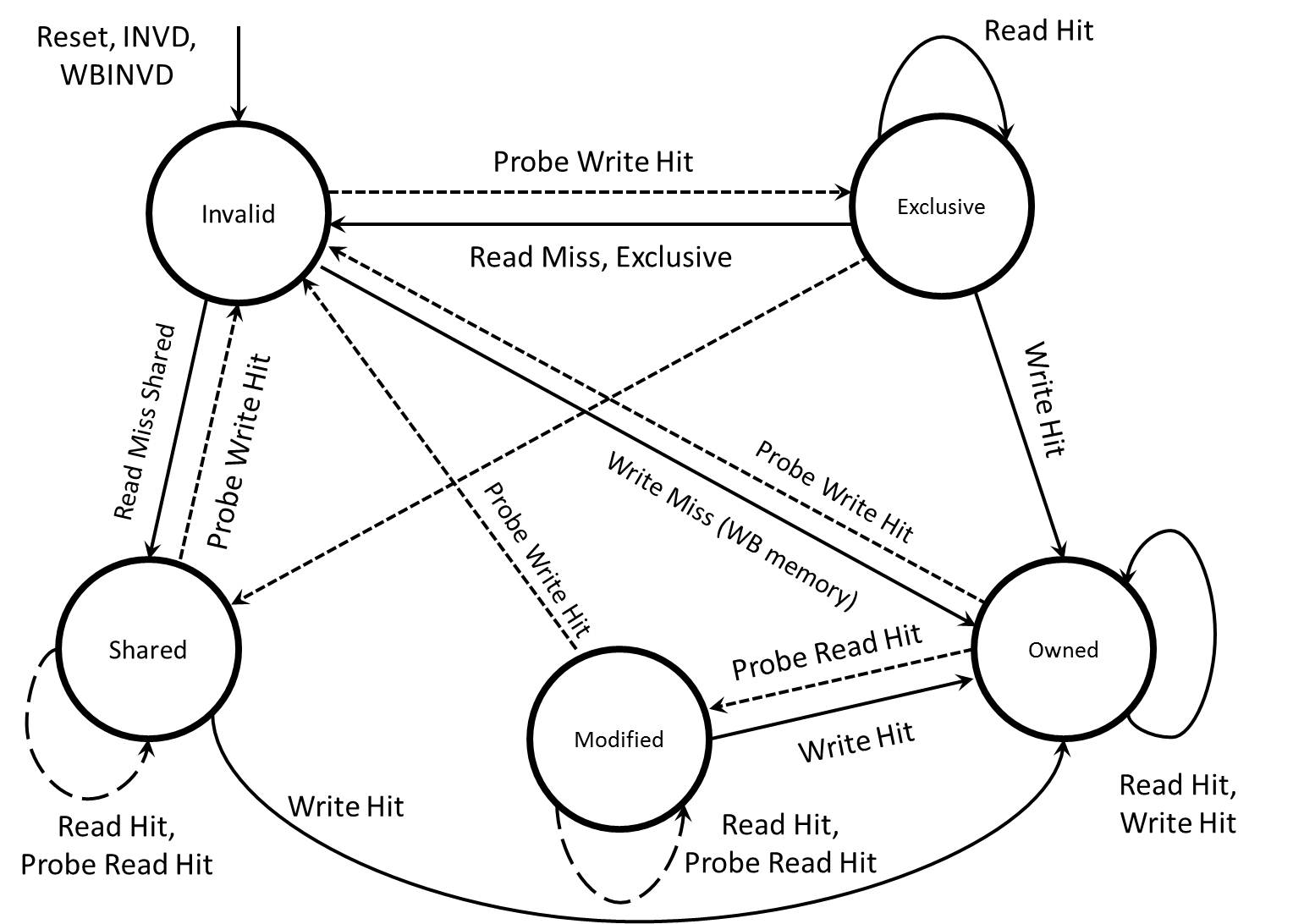

MOESI

MESIF

Protocol Performance