Chp8 my: Difference between revisions

Jump to navigation

Jump to search

| Line 26: | Line 26: | ||

[[Image:MESI.jpg]] | [[Image:MESI.jpg]] | ||

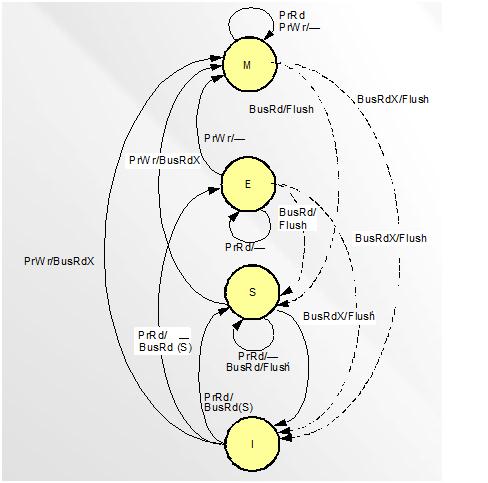

This figure shows the status change when bus traction generated. | This figure shows the status change when bus traction generated. | ||

====Intel==== | ====Intel==== | ||

Revision as of 01:10, 26 March 2010

In computing, cache coherence (also cache coherency) refers to the consistency of data stored in local caches of a shared resource. Cache coherence is a special case of memory coherence.

Cache Coherence

Definition

Coherency protocol

MSI protocol

Intel

AMD

MESI protocol

In MESI protocol, there are four cache block status:

- 1. Modified (M): the cache block valid in only one cache and the value is like different from the main memory.

- 2. Exclusive (E): the cache block is valid and clean, but only resides in one cache.

- 3. Shared (S): the cache block is valid and clean, but may exist in multiple caches.

- 4. Invalid (I): the cache block is invalid.

This figure shows the status change when bus traction generated.

Intel

AMD

MOESI protocol

Intel

AMD

AMD Opteron is using MOESI protocol for cache sharing.